Who develop I²C?

In early 1980’s PHILIPS designed & develop a new type of BUS standard named I2C for easy communication between integrated circuits especially in TV circuits, which exist on the circuit board. The name I²C translates intro (Integrated Circuits Bi-Directional 2 wire BUS standard for efficient inter IC control, commonly known as Inter-IC or I2C BUS.

When connecting a multiple devices together, the address and data line of each device were connected individually. This would result in a lot of traces on the PCB Board, and requires more components, this makes the system expensive and also vulnerable to interference and disturbance by (EMI)ELECTROMAGNETIC INTERFERENCE and ESD (ELECTROSTATIC DISCHARGE). The I2C now came up to the picture the I2C BUS standard is a remedy to this problem.

What is I²C Bus?

I2C is a serial communication bus protocol that has multi-master, low bandwidth, short distance communication bus protocol, commonly use in embedded systems, mobile phones, computers, automotive electronics, and communication devices. I2C provides advance features and much higher speed, simplicity and flexibility that makes attractive to consumer.

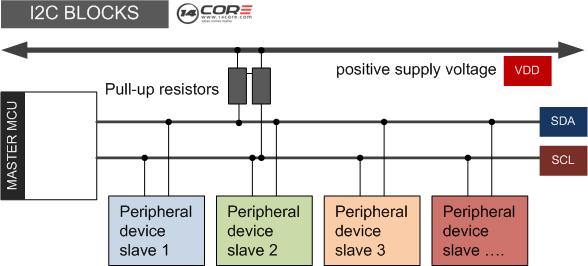

The basic design of I2C has a 7bit address space with 16 reserved address, which make the maximum number of nodes that can communicate on the same bus as 112, each I2C devices is recognized by a unique 7bit address. The two bi-directional lines, which carry information between the devices connected to the bus, are known as SDA(Serial Data Line) and SCL(Serial Clock Line) indicates that the SDA line contains a DATA and the SCL is a clock signal for synchronization commonly used voltage use for this 2wire are +5 volts or +3.3 volts. Compare to CAN& LIN protocols the I2C also follows the master & slave communication protocol but the I2C is a multi master bus it means it has more than one IC device capable of initiating a data transfer can be connected. The device that initiates the communication is a MASTER whereas the device being addressed by the MASTER is a SLAVE, each master device do generate clock signals which means each master generates its own clock signals when transferring data to the BUS.

The I2C Blocks Diagram.

Establishing a communication on I2C BUS.

Establishing a communication using I2C BUS it will wait until it sees no activity on the BUS if the SDA and SCL lines are both high then BUS is free.

The Master Microcontroller issues a condition that knows specific signal will be communicated to start to use the BUS. This condition informs all the slave devices to listen on the serial line. The SCL(Serial Clock Line) will be used by all the ICS as time reference, each bit of data on the SDA line will be valid before it can be used along with data line must be valid at the time the clock line switches from LOW to HIGH.

The master MCU will sends a unique binary address to the target device to access, then the master MCU will sign a one bit message named READ/WRITE flag on the BUS before it can SEND or RECEIVE data from the other chip. This read/write flag is an indication to the slave node to read or to write operation.

The slave node IC will compare the received address to its own address then the slave device will acknowledge signal if they are the same matching address. If the address doest not match they simply wait until the BUS is releasing a stop condition.

Once the master MCU receives the acknowledgement signal from the slave. it starts transmitting or receiving the data communication between the MASTER and SLAVE BUS, both Master and Slave can receive or transmit data depending on the communication (READ or WRITE). If the transmitter sends 8-bits of data to the receiver it will reply a 1 bit acknowledgement then the action data transfer will continues.

When the communication is complete the MASTER will sends signal to stop the condition indicating that everything is done. This action free ups the BUS the stop signal is a one bit of information transferred by WIGGLING of the SDA/SCL wires of the BUS.

NOTE: The devices & MASTER can identify themselves to each, and they can identify there specific MASTER drives and work their own specific address and functionality and only 2 devices can talk to each other during one conversation.

The I2C BUS interface is built around an input buffer and an open drain transistor, when the BUS is idle state of the BUS lines will keep in the logic HIGH state. The external Pull-up resistors are used for this condition to achieve. This pull-up resistor is actually a small current source if the device wants to put a signal in the BUS, the chip will drives its output transistor and pulling the BUS into LOW level. for example if the BUS is occupied already by another chip by sending a LOW state to the BUS, then all other chip lose their access to the BUS. The chip itself has a built-in BUS mastering technique.

Both SDA and SCL Bus are initially bi-directional. This means that in a particular device, these lines can be driven by the IC itself or from an external device in order to achieve this feature these signals use open collector or open drain outputs.

The open collector technique is an lengthy BUS the speed of transmission comes down due to the presence of capacitive load. The shapes of the signals alter in proportion to RC time constant. Higher the RC constant, the slower will be the transmission on this point the ICs will not be able to sense the logic 1 and 0, also it can cause reflection at high speed, which creates a GHOST SIGNAL and corrupt the data which is being transmitter.

Using active I2C terminator can overcome this problem. This device has a twin charge pump, which can be a dynamic resistor instead using a passive pull-up resistor. The moment the state charges provides a large current a low dynamic resistance to the bus. This action will charge the parasitic capacitor very quickly ones the voltage has risen a certain level, the high current mode cuts out the output current drops sharply.

Pingback:Starters #20 Wiring the I2C DS1307 Real Time Clock on Arduino | 14Core.com